-

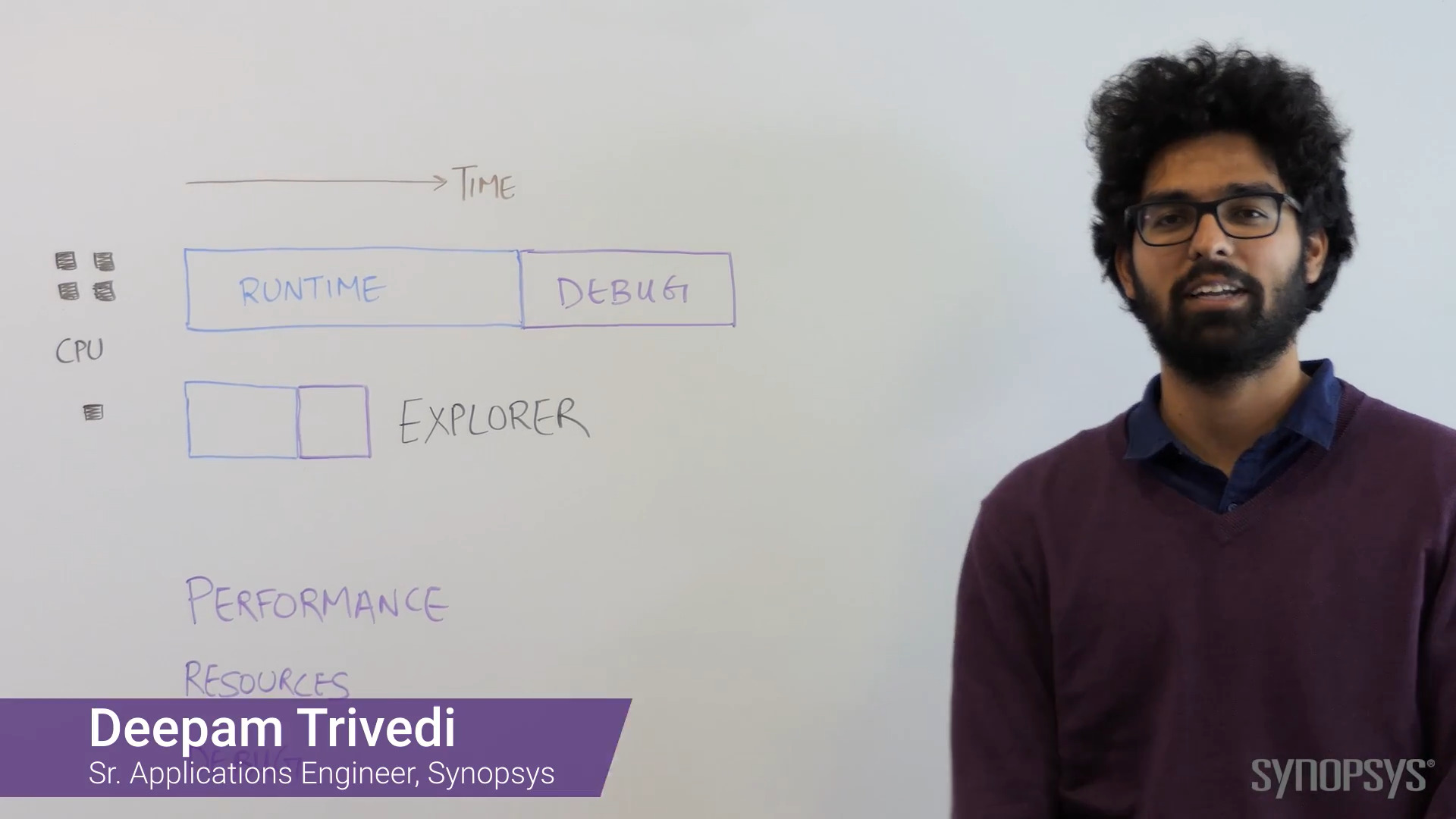

Play video 01 - How to Accelerate DRC Checking During SoC integration

01 - How to Accelerate DRC Checking During SoC integration

IC Validator Explorer is an innovative technology for design verification during SoC integration, enabling designers to run DRC faster and isolate gross design weaknesses within hours instead of days.

2:16

-

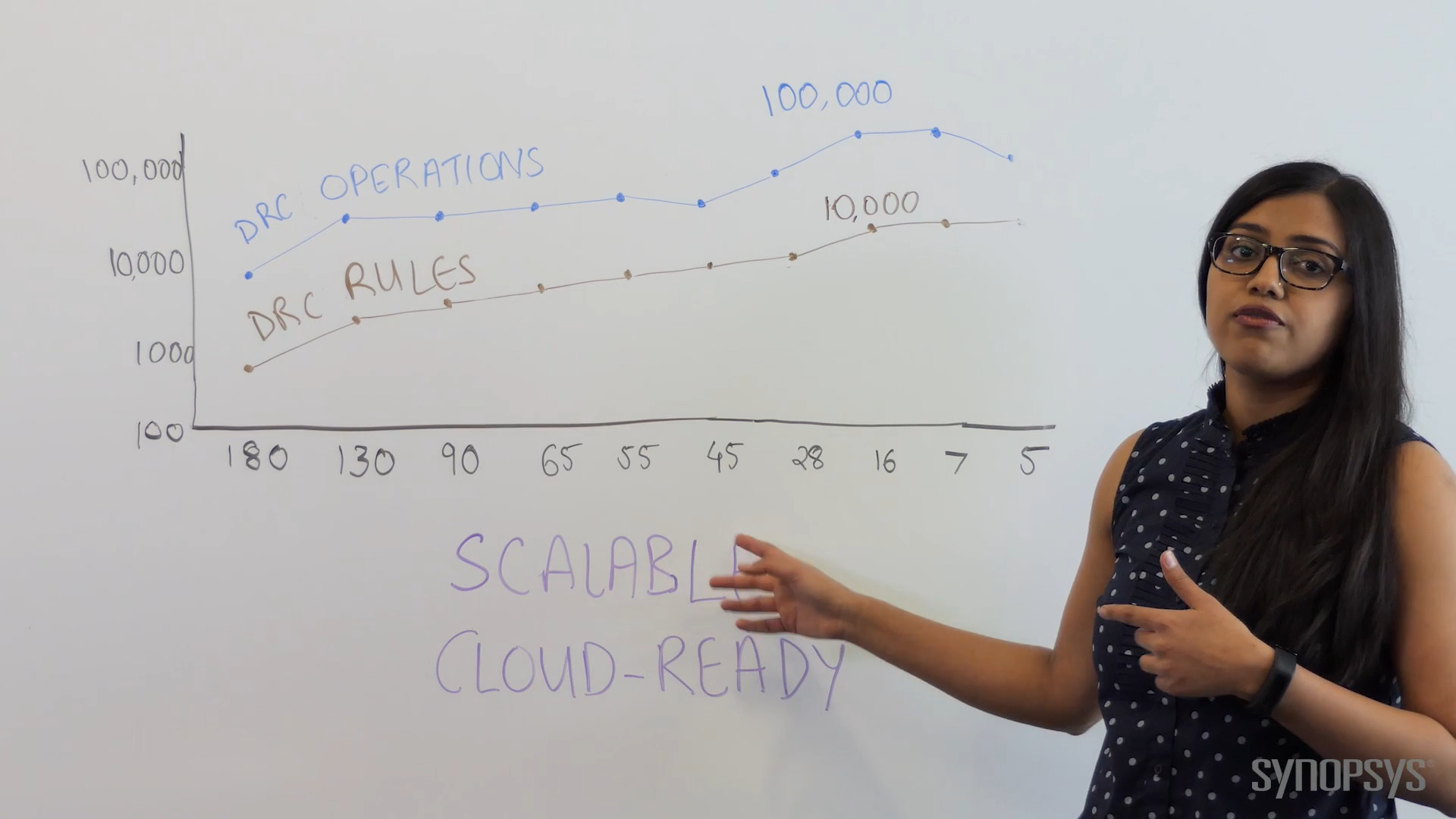

Play video 02 - How to Address Physical Signoff TAT Challenges for Today’s Advanced Node Designs

02 - How to Address Physical Signoff TAT Challenges for Today’s Advanced Node Designs

Physical verification runtimes are exploding at advanced technology nodes due to increasing design sizes and growing manufacturing complexity. Learn about how the IC Validator technology improves physical verification productivity.

5:59

-

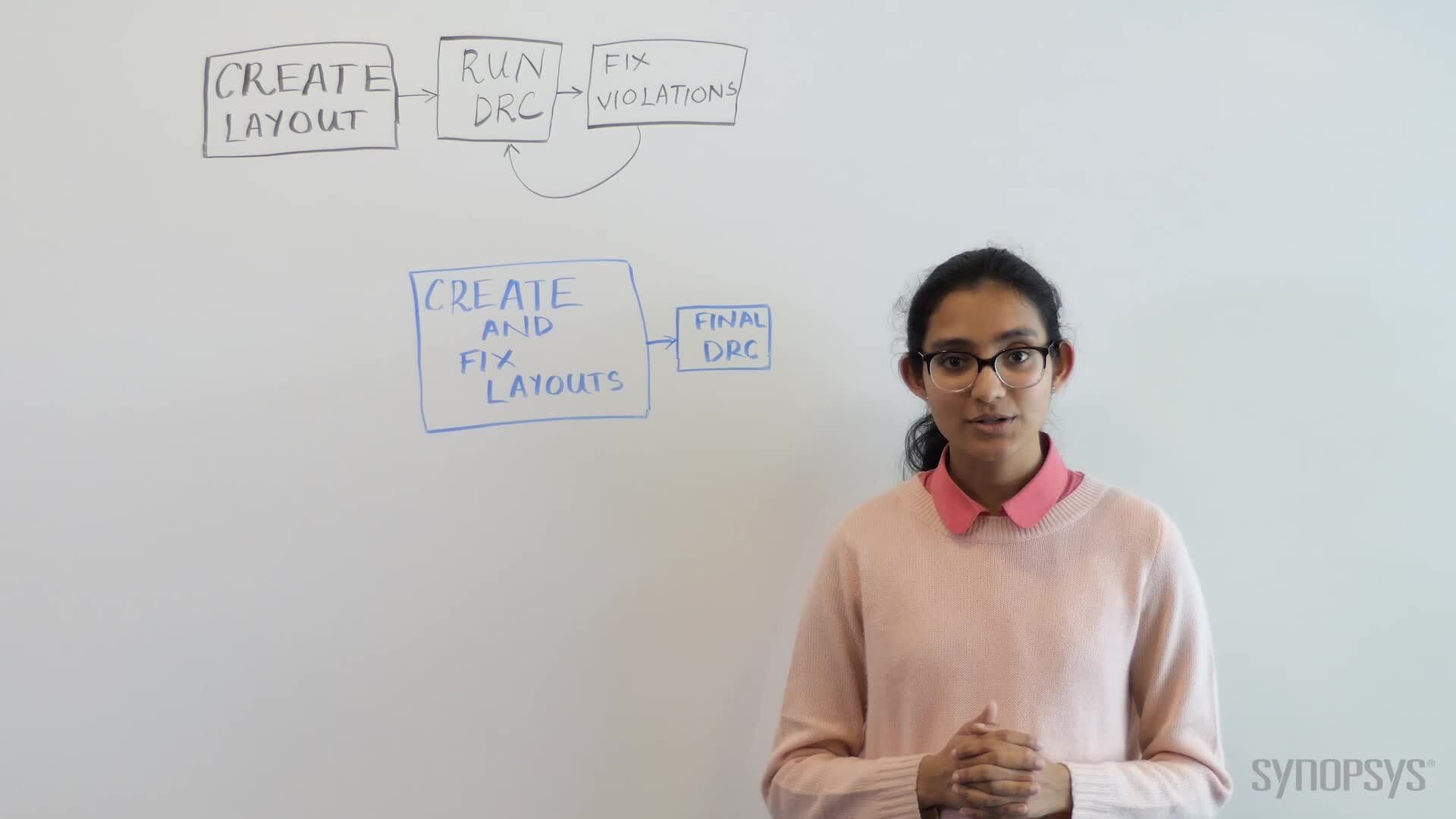

Play video 03 - How to Do On-demand Signoff DRC Checking for Custom Design Flows

03 - How to Do On-demand Signoff DRC Checking for Custom Design Flows

For custom layout design flows, designers need immediate and on-the-fly DRC feedback as they do the layout edits. IC Validator Live DRC checking offers signoff quality DRC checking directly within the layout design environment.

3:32

-

Play video 04 - Minimize the effect of metal fill on timing

04 - Minimize the effect of metal fill on timing

How to minimize the impact of Metal Fill on Timing? Metal fill insertion affects timing because of added capacitance. Balancing density requirements and timing on critical nets is crucial for timely design closure.

3:46

-

Play video 05 - How to reduce the amount of time to fix DRCs near tapeout?

05 - How to reduce the amount of time to fix DRCs near tapeout?

In the later stages of design cycle, it is important to identify and fix DRC issues quickly to meet the tapeout schedule. This video discusses some techniques and best practices.

3:32